Service hotline 0755-83261303

Email:ht@htsemi.com

Address315 Huachang Road, Dalang Street, Longhua District, Shenzhen

芯片怎么设计?

发表时间:2022-07-07

发表时间:2022-07-07 浏览量: 1235

浏览量: 1235

一枚芯片的生成,包括芯片设计、晶圆制造、封装测试三个环节。芯片的设计就处于芯片萌芽的最前端。

而芯片设计行业需要与产业链后端晶圆制造、封装测试环节紧密合作,不但在设计阶段需要考虑工艺是否可以实现相应电路设计,同时需要整合产业链资源确保芯片产品的及时供给,因此还十分考验企业的能力,是否能完成这一系列的生产。金誉半导体能够为客户提供一站式的应用解决方案和现场技术支持服务。

芯片中含有成千上万个PN结、电容、电阻、导线等,因此芯片设计是属于典型的技术密集型行业,非常考验工程师的技术能力,因为工程师的设计水平较大程度上决定了芯片的性能、功能、成本等核心因素。

图片来源网络

芯片设计最开始需要明确芯片的用途、规格和性能表现,让工程师根据芯片的特点将芯片内部的规格使用划分出来,规划每个部分的功能需求空间,确立不同单元间连结的方法,同时确定设计的整体方向。这一部分看似没有太多技术含量,却对之后的设计起着至关重要的作用,区域划分不够的,无法完成该区域内的功能实现,会导致之前的工作全部推翻重来。

然后基于前期的规格定义,明确芯片架构、业务模块、供电等系统级设计,例如CPU、GPU、NPU、RAM、联接、接口等。芯片设计需要综合考量芯片的系统交互、功能、成本、功耗、性能、安全及可维可测等综合要素。

接下来设计人员根据系统设计确定的方案,针对各模块开展具体的电路设计,使用专门的硬件描述语言(Verilog或VHDL),对具体的电路实现进行RTL(Register Transfer Level)级别的代码描述。代码生成后,就需要严格按照已制定的规格标准,反覆的确定此逻辑闸设计图是否符合规格并修改,直到功能正确为止。

之后,用逻辑综合工具,把用硬件描述语言写成的RTL级的代码转成门级网表(NetList),以确保电路在面积、时序等目标参数上达到标准。逻辑综合完成后需要进行静态时序分析,套用特定的时序模型,针对特定电路分析其是否违反设计者给定的时序限制。整个设计流程是一个迭代的流程,任何一步不能满足要求都需要重复之前的步骤,甚至重新设计RTL代码。

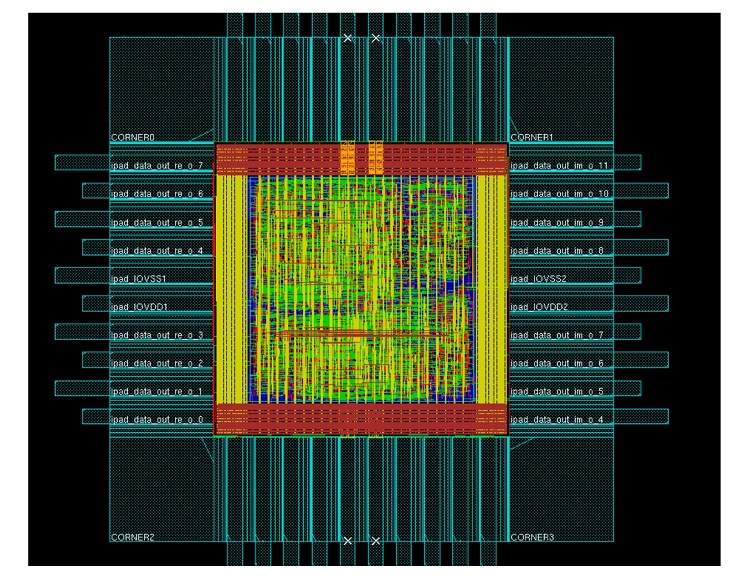

图片来源网络

最后,根据网表(NetList)所给定大小的硅片面积内,对电路进行布局和绕线,再对布线的物理版图进行功能和时序上的各种验证,这也是一个迭代的流程,验证不满足要求则需要重复之前的步骤,最终生成用于芯片生产的GDS(Geometry Data Standard)版图。

值得注意的是,芯片设计时需要考虑许多变量,例如信号干扰、发热分布等。而芯片的物理特性,如磁场、信号干扰,在不同制程下有很大不同,只能依靠EDA工具一步一步设计,一步步模拟,不断取舍。

每一次模拟之后,如果效果不理想,就要重新设计一次,通过检查、仿真、原型平台等手段反复迭代验证,它不是在设计完成后再进行的工序,而是贯穿在设计的每一个环节中的重复性行为。为的就是提前发现系统软硬件功能错误,进一步优化性能和功耗,使设计精准、可靠,并且符合最初规划的芯片规格,这对团队的智慧、精力、耐心都是极大考验。

Recruitment

0755-83240725

Cooperation

QQ:3001784606

3001784606

Tel

0755-83261303

Message